PIC AVR 工作室->TopPage->実験くん->MY FIRST FPGA

初めてのFPGA

まだ実験中です。ちょっとずつ書き進めていきます。

経緯

買ってから数年放置してきた「FPGAボードで学ぶ論理回路設計

」(解説本+テストボードのセット)ですが、

最近になってようやく動作確認が取れました。調子に乗ってもう少し首を突っ込んでみたくなったのが今回の経緯。

いずれにしても、私は根っからのソフト屋。FPGAやCPLDについては全くの素人。このテストボードを使って、 かるーく、かるーく実験をすすめていきたいと思います。(あまり参考にならないかもしれませんが…)

「汎用オペアンプでビデオ信号」の似非論文形式とは趣きを変えて、日記形式で私の頭の中の様子を書き出していきたいと思います。 私のような根っからの「ソフト屋さん」にとって、FPGAやCPLDが「ソフト開発」とどんな風に違うのか、私の頭で 気付いたことを書き記して行きたいと思っています。これから手をつけたいと考えている人にお役に立てれば幸いです。

第1日目

まず最初に、付属の解説本にしたがって統合環境「Quartus2」のインストールをしました。数年前と違って、今回は 上手く行きました。

実は、数年前に購入した時に放置した理由は、この統合開発環境ソフトのライセンス関係でコンパイル時にエラーが出たためなのでした。 Altera社からライセンスを取得し、メールで送られてくるライセンスファイルを使うことで認証ができるのですが、 コンパイル時にこのライセンスでエラーが出たようで、先に進めなかったんです。

というのも、私は以前より2台のPCを使い分けていて、1台はメール送受信やブラウズ、このサイトの更新などのような 一般的な(処理の軽い)用途に使うPCで、当時のOSはwindows-ME。もう1台はビデオ編集やその他の重たい処理用途に 使うPCで、当時のOSはwindows2000。

が、Quartus2はNT系(2000とかXPとかVISTAですね)じゃないと動かないのに、一方、メールはME搭載のPC でしか使えません。

Alteraのサイトで登録手続きをした際に、ライセンスはそのPCでしか使えないような仕組みを行っている ようなのですが、私のようにメールを使うPCとインストール先が異なる場合、上手く認証が通らなかったようです。

現在は、2台ともOSを入れ替えてしまったので、メール送受信用のPCでもQuartus2が動くはずだと気付き、 実際やってみたら動きました!これで1歩前進です。

さて、インストールが完了して初日にやってみたことはというと…「HELLO WORLD」ならぬ日の字型LEDへの 「数字の表示」でした。使ったVHDLのソースはこんな感じです。 (クリックすると別窓で開きます)

まさに日の字型LEDに数字を表示するだけです。極めて静的。何の動作もありません。FPGAに書き込み(ダウンロード)をすると、 数字の2が表示されるだけの物です。

まぁ、ひとまずHELLO WORLDが出来たと一安心した直後、VHDLの内容について考え直してみて大変なことに気付きました。

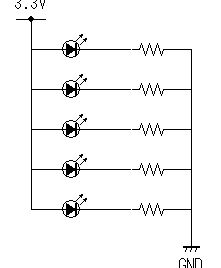

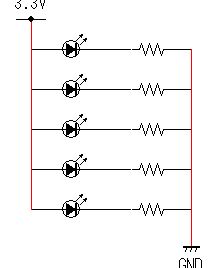

日の字型LEDで数字の2を表示するには5個のLEDをONにするわけです。回路図で言うとこういう感じです。

つまり、単純に5個のLEDを静的に光らせているだけ。

電源、LED、抵抗等はテストボード上にもともと組み込まれているわけだから、それって…冷静に考えると、 恐ろしいことに気付くわけです。つまり、今回のVHDLで実現できたことはというと…

この図の赤い線の部分だけのはず…。 それに気付いた時にぼう然としてしまいました…。 …結構苦労したのに、出来たことは 単なる配線だけだったのか…(TへT)

付属本の解説、P44曰く、

「ハードウェアの基本は同時処理」

と書かれています。そしてさらに、

「物理的に考えると、同時に実行されるということは、配線であると考えられます。電気的に伝達する信号を記述する、

それがハードウェアの基本概念になります。」

というこのページの最後の数行。まさにそういうことなのですね…。当たり前といえば当たり前なのですが、結構苦労したのに

その成果がたかが数本の配線だったとは…ショボン。

べらぼうめぇ。今日はこの辺で勘弁しておいてやろう、と思う私なのでした。

BREAK TIME

今回使用しているFPGAボード。配線も何もかも完了していて、実験で使用するにはとても便利なのですが、1つだけ難点が。

FPGAはCPLDと異なり、電源を切ると情報がすべて揮発してしまいます。通常は、不揮発ROM(EEPROMなど)に データを書き込んでおいて、立ち上げ時にそのデータをFPGAに書き込んでから実行するという仕組みを使います。

ですが、今回使用しているボードはこの不揮発ROMがついてません。なので、電源を切るたびにメモリが揮発してしまいます。 外部機器と接続してテストというには少々不便だなぁと。

まぁ、学習用ボードなので、これで充分といえば充分なのですが…。

第2日目

45ページ目からのpractice4に進みました。

これまでは止まった状態の配線を行っていましたが、practice4では水晶発振器からのパルスを入力にして、動くデモを 行うようです。

水晶発振子は33MHz。この立ち上がりエッジを捕まえて25ビットカウンタでカウントすると、およそ1秒が 得られるとの事。うん。それ自体は難しい話じゃないな。

で、VHDL自体はというと…。新たに出てきたVHDL命令は、

- if文

- 'event

- 加算演算子

です。加算演算子は、加算を行うためのライブラリを使用して整数の加算を簡単に行うためのモノだそうです。 if文は、評価式にプライオリティーがある条件判断を行うものだそうです。'eventは、信号に変化が 有った時にイベントが発生し、そのイベントをトリガとしてif文などによってカウンタの加算を行ったりすることができるようです。

実際にスクリプトを書いてコンパイル、実行してみたんですが、日の字型LEDに0~Fの16進の数値が 表示されるという結果が簡単に得られました。ふむふむ。

VHDLのスクリプトを読んでみるとほぼ理解できるんですが、新たな疑問も多々…。

- 加算演算子を使うには、それを含むライブラリを読み込まないとならないことは分かったんだけど、 じゃぁ、世の中にはどんなライブラリがあるのか?どうやって調べればいいのか?無料で使えるものは?有料のものは?(いわゆるIPね)

- if文の「評価式にプライオリティーがある」っていうのは、case文と具体的にナニが違うの?

- 'eventって、立ち上がり立下りエッヂ以外にどんなモノが使えるの?

- 今回のスクリプトって、FPGAリソースのどの程度を使用したの?

等など。いずれにしても、入門の入門であるこの本(とキット)では、そこまで言及されていないようです。残念…。 まぁ、追々調べていくことにしましょう。ひとまずは、配線だけでない、「動く成果物」を得られて一満足といった 感じです。

この次のpractice5は…スイッチのon/offとgeneric文。スイッチのon/offはクロックの入力と大差ないし、 generic文は…C言語で言う#defineと似たもんですね…。

BREAK TIME

さて今回のpractice4の実験。やってみて幾つかのモヤモヤが残りました。うーん、それがなぜ心に引っかかっていいるのか、 風呂に入りながらぼんやり考えていたんですが、ハッと気付きました。何がそんなに引っかかっていたのかを。

if文とか、'eventとかって、電子回路では一体どんな風に実現されるんだろう?っていうこと。

つまり、そういうことが腑に落ちてしっくり出来る状態でなければ、何か有った時に困っちゃうんじゃないか?と。

例えばコンパイルやフィッティングでエラーになって合成不可になっちゃったら、なぜ合成が出来ないのか? どうすればいいのか?を自分で解決できないだろうって思ったのです。(単純な文法エラーならどうにでもなるんですが)

VHDLやverilogHDLって、実際のハードウェアと比べるとかなり抽象的な表現になっているじゃないですか。 それゆえ、実際の電子回路のイメージがつきにくいんですよね。

そういえば、そもそもFPGA(やCPLD)を構成している基本素子がどうなっているのかとか、それらの素子がどんな回路で 繋がっているのかとか、そういう仕組み的なことも実はまだよく解ってないんですよね…。

多分、そういう細かいことが気になる性質なんでしょうね。いわゆる取り越し苦労?

まぁ、問題が起こる前から気になってしまうのが多分私の欠点であり、トラブルを先回りして解決しておきたいという利点でもあり…。

ふと自分の性格を思い出しなおすきっかけになってしまった…。そうそう。もっと気楽に。所詮実験ボードなんだし。とにかく先に進もう。 そして何か起こってから考えよう。ナニが気になっていたのかさえ気付いてしまえばもう安心。そう、先に進もう。進んで躓いたら考えよう。

何が気になっているのかに気付かないまま先に進むのは怖いけど、何が気になっているのかにさえ気付いてしまえば、 躓いてから振り返っても済む話でしょう。

人からもよく言われるように、「のんきで楽天家」なのも私の最大の利点なんだし…。

… 続きます …